METODO DEL CIRCUITO SEQUENZIATORE CON L'UTILIZZO DI VALVOLE MONOSTABILI

Aggiornato con un esempio

Per ottenere un circuito costituito da moduli sequenziatori con l'utilizzo di valvole monostabili, conviene effettuare una sequenza di memorie che si attivino permanentemente una di seguito all'altra, ciascuna settata da uno specifico segnale di settaggio e dalla attivazione della memoria precedente. Le memorie vengono poi resettate in cascata dall'ultimo segnale del ciclo.

Sequenza di memorie in accumulo, resettate da un unico segnale di fine ciclo

Si vogliono ottenere n segnali di uscita U1,U2,U3,...,Un che vengano attivati, uno di seguito all'altro da rispettivi segnali di settaggio .

Ciascuna uscita deve rimanere attivata fino a che non ne viene eccitata l'ultima . Questa dovrà resettare, in cascata, tutte le precedenti uscite e sé stessa, rispettando il precedente ordine di settaggio.

Sequenza di memorie in accumulo, resettate da un unico segnale di fine ciclo

Si vogliono ottenere n segnali di uscita U1,U2,U3,...,Un che vengano attivati, uno di seguito all'altro da rispettivi segnali di settaggio .

Ciascuna uscita deve rimanere attivata fino a che non ne viene eccitata l'ultima . Questa dovrà resettare, in cascata, tutte le precedenti uscite e sé stessa, rispettando il precedente ordine di settaggio.

Per ottenere le n uscite che rispettino i requisiti richiesti, occorre l'utilizzo di n-1 memorie, le quali vengano settate, una alla volta, da una successione di segnali di settaggio S1,S2,S3...Sn-1 che forniscono rispettivamente i segnali di uscita U1,U2,U3,...,Un-1, i quali permangano attivati, fino a che non venga settato, con Sn, l'ultimo segnale di uscita che resetti in cascata i precedenti segnali di memoria e per ultimo sé stesso.

Si indichi con Ui il segnale di uscita della memoria generica i. Questa deve essere attivata dal segnale di settaggio Si e rimanere tale solamente se è attivata la memoria precedente.

Deve risultare:

Deve risultare:

| Ui=(Si+Ui)·Uì-1 | 1 |

Si osservi che Ui-1 è in forma vera e non negata, per cui il segnale rimane attivo fino a che lo è il segnale di memoria precedente.

La prima memoria deve essere diversa dalle altre: essa è attivata dal primo segnale di settaggio Si e disattivata dall'ultimo segnale di uscita Un.

| U1=(S1+U1)·NOT Un | 2 |

Il segnale di resettaggio è indicato dalla sua etichetta preceduta dal NOT: NOT Un

I segnali di uscita dalla sequenza di memorie in accumulo, fino alla memoria n-1 risultano:

| U1=(S1+U1)*NOT Un | ||

| U2=(S2+U2)*U1 | ||

| .................................. | 3 | |

| Ui=(Si+Ui)*Ui-1 | ||

| .................................. | ||

| Un-1=(Sn-1+Un)*Un-2 |

L'ultimo segnale di uscita Un è di breve durata. Esso è attivato dall'ultimo segnale di settaggio del ciclo Sn e dalla attivazione del segnale di memoria Un-1; dà il comando dell'ultimo passo, resetta la prima memoria U1, e con essa in cascata tutte le altre memorie.

| Un=Sn·Un-1 | 4 |

Il segnale Un non proviene da una memoria. Esso è attivo solamente quando lo sono il segnale di memoria precedente e il segnale di settaggio Sn

Si noti, osservando le espressioni (3), che Un resetta la memoria U1 . Disattivata questa si disattiva la U2, la quale disattiva la U3, così via...

Quando la Un disattiva la U1, in cascata vengono disattivate tutte le altre, fino alla Un-1, . questa poi disattiva la Un, anche se rimane attivato il segnale di settaggio Sn-1 .

Riassumendo le equazioni logiche della sequenza delle memorie in accumulo:

Si noti, osservando le espressioni (3), che Un resetta la memoria U1 . Disattivata questa si disattiva la U2, la quale disattiva la U3, così via...

Quando la Un disattiva la U1, in cascata vengono disattivate tutte le altre, fino alla Un-1, . questa poi disattiva la Un, anche se rimane attivato il segnale di settaggio Sn-1 .

Riassumendo le equazioni logiche della sequenza delle memorie in accumulo:

| U1=(S1+U1)·NOT Un | ||

| U2=(S2+U2)·U1 | ||

| .................................. | ||

| Ui=(Si+Ui)·Ui-1 | 5 | |

| .................................. | ||

| Un-1=(Sn-1+Un)·Un-2 | ||

| Un=Sn·Un-1 |

La sequenza di memorie descritte può essere utilizzata per l'elaborazione dei comandi delle fasi di un ciclo con l'utilizzo di elettrovalvole monostabili.

Il metodo si può riassumere nei seguenti punti:

Il metodo si può riassumere nei seguenti punti:

- Ad ogni passo si associa una memoria con precedenza alla cancellazione, che viene attivata o dallasola variabile attiva o da tutti i finecorsa attivati (con autoeccitazione dato dal segnale di memoria stesso) e dal segnale di memoria precedente, dipendente da di tutti i finecorsa già attivati.

In tal modo, anche se si presenta nel ciclo una ripetizione della combinazione dei finecorsa, in passi diversi, in questi viene attivata una memoria diversa, dipendente dal segnale di memoria precedente.

Quindi in passi diversi la stessa combinazione dei finecorsa attiva una memoria differente, che rimane attiva fino al l'ultimo segnale di comando del ciclo .

Consideriamo così il ciclo A+ B+ B¯ A¯

Ai passi del ciclo si associ la sequenza di memorie in accumulo precedentemente descritta, i cui segnali di settaggio siano dati dalla combinazione dei finecorsa toccati all'inizio del passo.

A+=ao·bo ---> Us1 B+=a1·bo ---> Us2 6 B¯=a1·b1 ---> Us3 A¯=a1·bo ---> Us4

Us4 è il segnale non di memoria da associare alla combinazione dei finecorsa dell'ultimo passo, che abilita questo e resetta sequenzialmente, dalla prima all'ultima, le memorie precedentemente settate

Le equazioni logiche dei segnali di memoria sono:

Us1=(ao·bo·Start+Us1)·NOT Us4 Us2=(a1·bo+Us2)·Us1 Us3=(a1·b1+Us3)·Us2 7Us4=a1·bo·Us3

Si noti che il segnale a1·bo risulta di settaggio sia Us2 sia di Us4.

Però quando si verifica per la prima volta la combinazione a1 · bo, nel II passo, si attiva solamente il segnale di memoria Us2, essendo già attivato Us1 (posto in AND con " a1 · bo+Us2"): non si attiverà Us4, non essendo ancora attivato Us3 .

Quando nel IV passo si presenta di nuovo la combinazione a1·bo allora si attiverà il segnale Us4 , essendo ora attivato Us3 .

Attivato il segnale Us4, questo, essendo posto al reset della memoria Us1, la disattiva. Allora, in cascata, la disattivazione di Us1 diseccita Us2, che disattiva la Us3, la quale in fine disattiva la Us4 completando il ciclo. - Il comando dei cilindri avviene attraverso il settaggio e resettaggio di elettrovalvole monostabili.

Nell'esempio considerato si associno:

Elettrovalvola Y1 ---> A+ A¯ Elettrovalvola Y3 ---> B+ B¯

- Il comando di ciascuna elettrovalvola monostabile si ottiene ponendo in AND i due segnali di memoria riferiti: uno all'attivazione dell'elettrovalvola posto in forma vera, l'altro alla disattivazione posto in forma negata.

- Così il segnale di comando dell'elettrovalvola , riferita ai passi del cilindro A, si ottiene ponendo in AND i due segnali:

Si ottiene:1. Us1 in forma vera, corrispondente ad A+ 2. NOT Us4 in forma negata, corrispondente ad A¯

Infatti nel I passo la combinazione dei finecorsa ao·bo attiva la memoria Us1, mentre Us4 è disattivata:Y1=Us1·NOT Us4 8

Risulterà:Us1=1 Us4=0

Y1 = 1·NOT 0 = 1·1 = 1 e si ha l'eccitazione dell'elettrovalvola Y1 con fuoriuscita dello stelo di A: A+ . L'elettrovalvola rimane eccitata fino a che permangono gli stati logici: Us1=1 Us4=0

Nel IV passo, quando per la 2° volta si attiva la combinazione a1·bo, viene attivato il segnale Us4, ed è ancora attivatoUs1 :

Risulterà:Us1=1 Us4=1

e si diseccita l'elettrovalvola Y1 con rientro dello stelo di A: A¯.Y1 = 1·NOT 1 = 1·0 = 0

- Alla stessa maniera si ottiene il segnale di comando dell'elettrovalvola Y3: è settata dal segnale Us2 e resettata da Us3. Risulterà:

Y3=Us2·NOT Us3 9 Le equazioni logiche delle memorie 7 possono essere espresse rispetto alle variabili attive, invece che alle combinazioni complete dei finecorsa attivati.Us1=(ao·Start+Us1)·NOT Us4 Us2=(a1+Us2)·Us1 10 Us3=(b1+Us3)·Us2 Us4=bo·Us3

Riunendo così le equazioni delle memorie e quelle dell'attivazione delle elettrovalvole si ha:

Us1=(ao·Start+Us1)·NOT Us4 Us2=(a1+Us2)·Us1 Us3=(b1+Us3)·Us2 11 Us4=bo·Us3 Y1=Us1·NOT Us4 Y3=Us2·NOT Us3

OCCUPAZIONI PLC

Ingressi I - Uscite O

COMPONENTE INGRESSO Start I0 Y1 O0 finecorsa ao I1 Y3 O1 finecorsa a1 I2 finecorsa bo I3 finecorsa b1 I4

| Funzionamento

| |||||||||||||||||

| ESEMPIO | ||||||||||||||||||

| Ciclo con ripetizione di comandi: | ||||||||||||||||||

| Una serie di pezzi, posti in posizione fissa entro un raccoglitore, debbono essere presi uno alla volta da una ventosa, innalzati, trasportati e depositati entro uno scatolone di imballaggio. Effettuare uno schema di massima del sistema ed elaborareil ciclo elettropneumatico occorrente per la presa del pezzo, il suo trasporto nello scatolone ed il deposito in questo. | ||||||||||||||||||

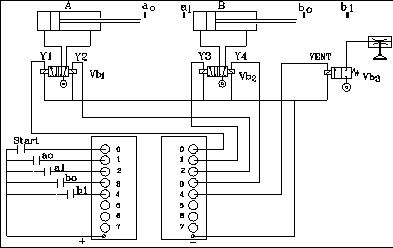

| Soluzione del problema La ventosa "VENT" Fig. E.1 viene posta all'estremità del cilindro pneumatico "B" a doppio effetto, istallato su una slitta orizzontale comandata da un cilindro pneumatico "A" a doppio effetto. | ||||||||||||||||||

| Fig. E.1 I cilindri "A", "B" sono comandati rispettivamente dalle ellettrovalvole bistabili: Vb1,Vb2 (schema Fig.E.2). I segnali di pilotaggio delle elettrovalvole sono elaborati attraverso i finecorsa ao,a1 posti alle estremità della corsa della slitta, comandata dal cilindro A, e bo,b1 posti alle estremità della corsa dello stelo del cilindro B, recante la ventosa utilizzata per prendere del pezzo dal raccoglitore e lasciarlo nello scatolone. | |||||||||||||||||

| Fig. E.2 | ||||||||||||||||||

| La ventosa è collegata ad un eiettore, costituito essenzialmente da un tubo di Venturi che genera un vuoto in corrispondenza del minimo diametro. L'eiettore viene posto all'uscita di una elettrovalvola 2/2 NC monostabile (Vb3), la cui bobina viene eccitata con il segnale di eccitazione, indicato con "VENT", che deve essere emesso quando, nella prima postazione P1, lo stelo del cilindro B è fuoriuscito e si comanda la corsa di rientro: B-. A questo punto si crea il vuoto nell'eiettore e la ventosa in prossimità del pezzo lo afferra e lo condurrà fino alla posizione di abbandono. | |||||||||||||||||

| L'elettrovalvola Vb3 dovrà diseccitarsi quando lo stelo del cilindro B, nella posizione P2, fuoriuscendo porta il pezzo in corrispondenza dello scatolone di imballaggio. | ||||||||||||||||||

| Sequenza ciclica Il ciclo elettropneumatico si compone delle seguenti fasi:

| ||||||||||||||||||

Occupazioni ingressi - uscite del PLC | ||||||||||||||||||

| ||||||||||||||||||

Soluzione con circuito sequenziale e utilizzo di elettrovalvole monostabili | ||||||||||||||||||

| Ai passi del ciclo si associa la sequenza di memorie in accumulo i cui segnali di settaggio sono dati dalle variabili attive all'inizio del passo. | ||||||||||||||||||

| E 2.1 | |||||||||||||||||

| Le equazioni logiche dei segnali di memoria in accumulo sono: | ||||||||||||||||||

| E. 2.2 | |||||||||||||||||

| Sia indicata con Y1 la bobina dell'elettrovalvola che comanda il cilindro A e Y3 quella di comando del cilindro B. Le equazioni logiche di comando di Y1,Y3 si ottengono dalle seguenti considerazioni: | ||||||||||||||||||

| ||||||||||||||||||

| E. 2.3 | ||||||||||||||||||

| ||||||||||||||||||

| ||||||||||||||||||

| ||||||||||||||||||

| Si ottiene: | ||||||||||||||||||

| E. 2.4 | ||||||||||||||||||

| ||||||||||||||||||

| E. 2.5 | ||||||||||||||||||

| ||||||||||||||||||

| E. 2.6 | ||||||||||||||||||

| ||||||||||||||||||

| E. 2.7 | ||||||||||||||||||

| ||||||||||||||||||

| E. 2.8 | ||||||||||||||||||

| ||||||||||||||||||

0 Comments:

Posta un commento